1. Getting Started¶

Microchip is running an Early Access Program (EAP) for the SmartHLS compiler software. This program enables you to evaluate a beta version of SmartHLS software and provide us with valuable feedback. To participate in EAP and download SmartHLS, please fill out the SmartHLS software request form here and we will contact you to support your evaluation.

1.1. Installation¶

SmartHLS supports Windows 10 and Linux (CentOS 7).

1.1.1. Windows¶

Run the Windows installer program, SmartHLS-2021.1.2-Win64-Setup.exe, and go through the steps in the installer.

1.1.2. Linux¶

1.1.2.1. CentOS¶

The CentOS installer is packaged as a self-extracting shell script that can be installed to a local directory. To run the installer:

cd $(INSTALLATION_DIRECTORY)

sh /path/to/smarthls-2021.1.2-centos-installer.run

This will install SmartHLS into the INSTALLATION_DIRECTORY. After the installation is completed, please add the SmartHLS bin directory to your path:

export PATH=$(INSTALLATION_DIRECTORY)/smarthls-2021.1.2/smarthls/bin:$PATH

1.1.3. Libero and ModelSim¶

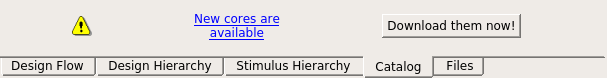

You will need to install the Libero SoC software to synthesize the generated hardware for Microchip FPGAs. After installing Libero, please make sure to download all of new IP cores (open a Libero project, go to the Catalog pane, and click on “Download them now!”, as shown below), as some IPs may be needed for SmartHLS.

Libero also comes with ModelSim which is used by SmartHLS to simulate the generated Verilog. Please note that the first time you simulate a generated hardware block with a fresh install of SmartHLS, ModelSim will compile our IP libraries, which may take some time.

1.2. Quick Start Tutorial¶

Please refer to our SmartHLS Tutorial for Microsemi PolarFire: Sobel Filtering for Image Edge Detection <https://www.microsemi.com/document-portal/doc_download/1245532-legup-hls-tutorial> on how to use some of the major features and optimization techniques of SmartHLS.