Overview¶

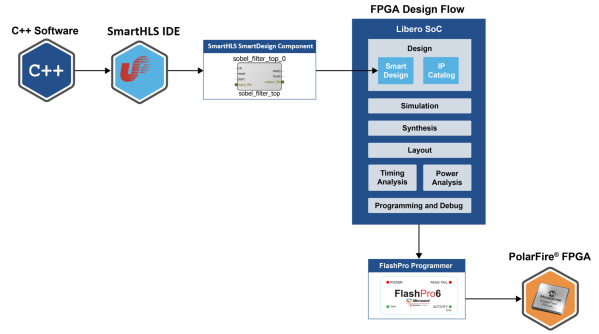

Smart high-level synthesis (SmartHLS) Compiler is an Eclipse-based integrated development environment that takes C++ software code as input and generates a SmartDesign IP component (Verilog HDL) as output. Hardware engineers can instantiate the generated SmartDesign IP component in the SmartDesign canvas available in Libero SoC design suite to build an FPGA system.

SmartHLS automatically compiles a C/C++ program into hardware described in Verilog HDL (Hardware Description Language). The generated hardware can be programmed onto an Microchip FPGA (Field-Programmable Gate Array). Hardware implemented on an FPGA can provide 2-10X performance and power benefits over the same computation running on regular processors.

SmartHLS includes C/C++ to Verilog high-level synthesis tool and is tested on Windows and Linux 64-bit Operating systems.

The following table describes each document shipped with SmartHLS.

Document Title |

Description |

|---|---|

Installation and a quick start guide |

|

How to use SmartHLS to generate hardware |

|

How to optimize the generated hardware |

|

Synthesized hardware architecture |

|

Pragmas manual |

|

Constraints manual |

|

How to obtain a free license for SmartHLS |

|

Supported FPGA devices |

|

Supported Libero version |

|

Frequently asked questions |

|

SmartHLS Migration Guide |

|

New features and known problems with each release |

|

How to create tech support cases and post to our forum |

For detailed trainings on using SmartHLS and example applications, see our GitHub Examples repository.